# **General Purpose EMI Reduction IC**

# **Description**

The P2008A is a versatile spread spectrum frequency modulator designed specifically for digital camera and other digital video and imaging applications. The P2008A reduces electromagnetic interference (EMI) at the clock source, allowing system wide reduction of EMI of down stream clock and data dependent signals. The P2008A allows significant system cost savings by reducing the number of circuit board layers ferrite beads, shielding and other passive components that are traditionally required to pass EMI regulations.

The P2008A uses the most efficient and optimized modulation profile approved by the FCC and is implemented in a proprietary all digital method.

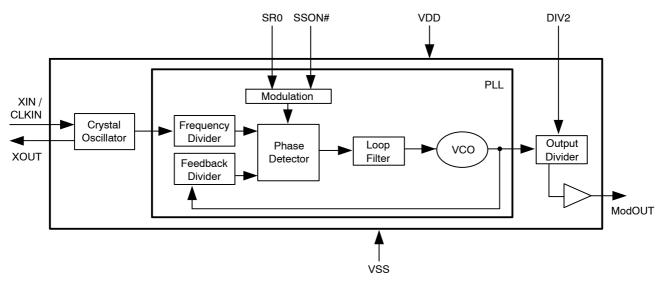

The P2008A modulates the output of a single PLL in order to "spread" the bandwidth of a synthesized clock, and more importantly, decreases the peak amplitudes of its harmonics. This results in significantly lower system EMI compared to the typical narrow band signal produced by oscillators and most frequency generators. Lowering EMI by increasing a signal's bandwidth is called 'spread spectrum clock generation.'

#### **Applications**

The P2008A is targeted towards cable, xDSL, fax modem, set-top box, USB controller, DSC, and other embedded systems.

#### **Features**

- FCC Approved Method of EMI Attenuation

- Provides up to 15 dB of EMI Suppression

- Generates a 1X or <sup>1</sup>/<sub>2</sub>X Low EMI Spread Spectrum Clock of the Input Frequency

- Input Frequency Range: 4 MHz to 32 MHz

- Internal Loop Filter Minimizes External Components and Board Space

- Spreading Ranges from ±0.8% to ±3.2%

- SSON# Control Pin for Spread Spectrum Enable and Disable Options

- Low Cycle-to-Cycle Jitter

- 3.3 V Operating Voltage

- Ultra-low Power CMOS Design

- Available in 8-pin SOIC and TSSOP Packages

- These are Pb-Free Devices

# ON Semiconductor®

http://onsemi.com

SOIC-8 S SUFFIX CASE 751BD TSSOP-8 T SUFFIX CASE 948AL

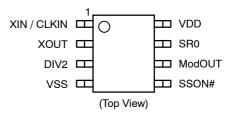

#### **PIN CONFIGURATION**

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.

1

Figure 1. Block Diagram

**Table 1. ABSOLUTE MAXIMUM RATINGS**

| Symbol               | Parameter                                             | Rating       | Unit |

|----------------------|-------------------------------------------------------|--------------|------|

| VDD, V <sub>IN</sub> | Voltage on any pin with respect to Ground             | -0.5 to +4.6 | V    |

| T <sub>STG</sub>     | Storage temperature                                   | -65 to +125  | °C   |

| T <sub>A</sub>       | Operating temperature                                 | 0 to +70     | °C   |

| T <sub>s</sub>       | Max. Soldering Temperature (10 sec)                   | 260          | °C   |

| $T_J$                | Junction Temperature                                  | 150          | °C   |

| T <sub>DV</sub>      | Static Discharge Voltage (As per JEDEC STD22- A114-B) | 2            | KV   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Table 2. DC ELECTRICAL CHARACTERISTICS

| Symbol           | Parameter                                                     | Min     | Тур  | Max     | Unit |

|------------------|---------------------------------------------------------------|---------|------|---------|------|

| V <sub>IL</sub>  | Input low voltage                                             | VSS-0.3 | =    | 0.8     | V    |

| V <sub>IH</sub>  | Input high voltage                                            | 2.0     | =    | VDD+0.3 | V    |

| I <sub>IL</sub>  | Input low current (pull-up resistors on inputs SR0 and DIV2)  | -       | -    | -35     | μΑ   |

| I <sub>IH</sub>  | Input high current (pull-down resistor on input SSON#)        | =       | =    | 35      | μΑ   |

| I <sub>XOL</sub> | XOUT Output Low Current (@ 0.4 V, VDD = 3.3 V)                | _       | 3    | -       | mA   |

| I <sub>XOH</sub> | XOUT Output High Current (@ 2.5 V, VDD = 3.3 V)               | _       | 3    | -       | mA   |

| V <sub>OL</sub>  | Output low voltage (VDD = 3.3 V, I <sub>OL</sub> = 10 mA)     | -       | -    | 0.4     | V    |

| V <sub>OH</sub>  | Output high voltage (VDD = 3.3 V, I <sub>OH</sub> = 10 mA)    | 2.5     | =    | =       | V    |

| I <sub>CC</sub>  | Dynamic supply current normal mode (3.3 V, and 15 pF loading) | 6.0     | 7.0  | 8.3     | mA   |

| I <sub>DD</sub>  | Static supply current standby mode                            | =       | 0.6  | =       | mA   |

| VDD              | Operating voltage                                             | 3.0     | 3.3  | 3.6     | V    |

| t <sub>ON</sub>  | Power up time (first locked clock cycle after power up)       | -       | 0.18 | -       | mS   |

| Z <sub>OUT</sub> | Clock output impedance                                        | -       | 50   | =       | Ω    |

#### **Table 3. AC ELECTRICAL CHARACTERISTICS**

| Symbol                   | Pa                        | Parameter                                     |    |     | Max | Unit |

|--------------------------|---------------------------|-----------------------------------------------|----|-----|-----|------|

| f <sub>IN</sub>          | Input frequency           | Input frequency                               |    |     | 32  | MHz  |

| f <sub>OUT</sub>         | Output frequency          | Output frequency DIV2 = 0                     |    | 10  | 16  | MHz  |

|                          |                           | DIV2 = 1                                      | 4  | 20  | 32  |      |

| t <sub>LH</sub> (Note 1) | Output rise time (measure | Output rise time (measured at 0.8 V to 2.0 V) |    |     | 1.1 | nS   |

| t <sub>HL</sub> (Note 1) | Output fall time (measure | Output fall time (measured at 2.0 V to 0.8 V) |    |     | 1.0 | nS   |

| t <sub>JC</sub>          | Jitter (cycle-to-cycle)   | -                                             | -  | 360 | pS  |      |

| t <sub>D</sub>           | Output duty cycle         |                                               | 45 | 50  | 55  | %    |

<sup>1.</sup>  $t_{LH}$  and  $t_{HL}$  are measured into a capacitive load of 15 pF.

#### **Table 4. PIN DESCRIPTION**

| Pin# | Pin Name    | Type | Description                                                                                                                                                                                                                                                                                                    |

|------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | XIN / CLKIN | I    | Crystal connection or external reference frequency input. This pin has dual functions. It can be connected either to an external crystal or an external reference clock.                                                                                                                                       |

| 2    | XOUT        | 0    | Crystal connection. If using an external reference, this pin must be left unconnected.                                                                                                                                                                                                                         |

| 3    | DIV2        | I    | Digital logic input used to select normal output mode or divide-by-two output mode. When this pin is HIGH, the frequency of the output clock is the same as the input clock frequency. When it is tied low, the output frequency is half the input clock frequency. This pin has an internal pull-up resistor. |

| 4    | VSS         | Р    | Ground to entire chip. Connect to system ground.                                                                                                                                                                                                                                                               |

| 5    | SSON#       | I    | Digital logic input used to enable Spread Spectrum function (Active LOW). Spread Spectrum function enabled when LOW, disabled when HIGH.  This pin has an internal pull-low resistor.                                                                                                                          |

| 6    | ModOUT      | 0    | Spread spectrum clock output.                                                                                                                                                                                                                                                                                  |

| 7    | SR0         | I    | Digital logic input used to select Spreading Range (Refer to Modulation Output and Spreading Selection Table.) This pin has an internal pull-up resistor.                                                                                                                                                      |

| 8    | VDD         | Р    | Power supply for the entire chip                                                                                                                                                                                                                                                                               |

# Table 5. MODULATION OUTPUT AND SPREADING SELECTION (ModOUT = XIN / CLKIN)

|     | Output Frequency Range DIV2 = 1 |        |        |        |        |        |        |                               |

|-----|---------------------------------|--------|--------|--------|--------|--------|--------|-------------------------------|

| SR0 | 8 MHz                           | 12 MHz | 16 MHz | 20 MHz | 24 MHz | 28 MHz | 32 MHz | Modulation Rate               |

| 0   | ±2.2%                           | ±1.8%  | ±1.2%  | ±1.1%  | ±1.0%  | ±0.9%  | ±0.8%  | (VIN / CLIVIN/00) * 60 F I/U- |

| 1   | ±3.2%                           | ±2.5%  | ±2.0%  | ±1.6%  | ±1.4%  | ±1.25% | ±0.15% | (XIN / CLKIN/20) * 62.5 KHz   |

# Table 6. MODULATION OUTPUT AND SPREADING SELECTION (ModOUT = $^{1}/_{2}$ XIN / CLKIN)

| SR0 | 4 MHz | 6 MHz | 8 MHz | 10 MHz | 12 MHz | 14 MHz | 16 MHz | Modulation Rate                |

|-----|-------|-------|-------|--------|--------|--------|--------|--------------------------------|

| 0   | ±2.0% | ±1.8% | ±1.2% | ±1.1%  | ±1.0%  | ±0.9%  | ±0.8%  | (VIN. / CLIZIN/00) * 60 F KLI- |

| 1   | ±3.2% | ±2.6% | ±2.0% | ±1.6%  | ±1.4%  | ±1.25% | ±0.15% | (XIN / CLKIN/20) * 62.5 KHz    |

#### **Spread Spectrum**

The Modulation Output and Spreading Selection Tables illustrate the two possible spread spectrum options. The optimal setting should minimize system EMI to the fullest without affecting system performance. The spreading is described as a percentage deviation of the center frequency (Note: The center frequency is the frequency of the external reference input on XIN / CLKIN, Pin1).

#### Example:

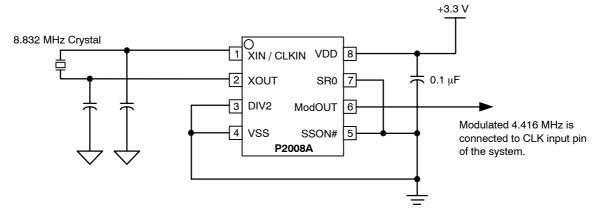

The P2008A is designed for communications, digital video and imaging applications. It is not only optimized for operation in the 4 MHz – 32 MHz range, but its output frequency can be extended down to one half of the input clock frequency using the divide-by-two feature. This feature extends low frequency as low as to 2 MHz. Setting Pin 3 low (DIV2 = 0; Divide-by-two mode) sets the output frequency (ModOUT) to half the frequency of the input

clock (XIN / CLKIN). This is a simple way to generate a spread spectrum modulated low frequency clock when only a higher frequency signal is available. If you want the output frequency to be the same as the input, you can either set DIV2=1 or leave it unconnected.

Selecting the P2008A's spread options is a matter of either setting SR0=1 or SR0=0. Setting SR0=0 set as a lower modulation spread, while setting it to 1 introduces a wider spectral spread in the output clock. Refer to *Modulation output and Spreading Selections* Tables. The example given in the figure below shows the device set to the divide-by-two mode (DIV2=0) with a lower spectrum range (SR0=0). The versatility provided by allowing both clock division and spread spectrum on one chip is already proving to be a popular solution among leading system manufacturers.

Figure 2. P2008A Application Schematic

# **PACKAGE DIMENSIONS**

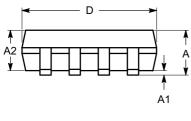

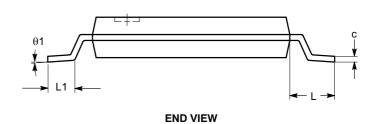

TSSOP8, 4.4x3 CASE 948AL-01 ISSUE O

| SYMBOL | MIN      | NOM  | MAX  |  |  |

|--------|----------|------|------|--|--|

| Α      |          |      | 1.20 |  |  |

| A1     | 0.05     |      | 0.15 |  |  |

| A2     | 0.80     | 0.90 | 1.05 |  |  |

| b      | 0.19     |      | 0.30 |  |  |

| С      | 0.09     |      | 0.20 |  |  |

| D      | 2.90     | 3.00 | 3.10 |  |  |

| E      | 6.30     | 6.40 | 6.50 |  |  |

| E1     | 4.30     | 4.40 | 4.50 |  |  |

| е      | 0.65 BSC |      |      |  |  |

| L      | 1.00 REF |      |      |  |  |

| L1     | 0.50     | 0.60 | 0.75 |  |  |

| θ      | 0°       |      | 8°   |  |  |

**SIDE VIEW**

#### Notes:

- (1) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC MO-153.

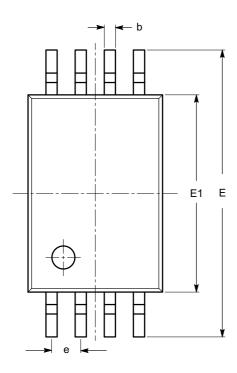

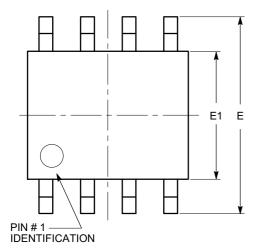

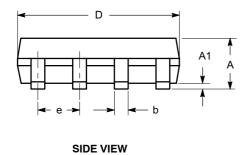

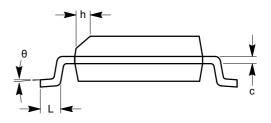

# **PACKAGE DIMENSIONS**

SOIC 8, 150 mils CASE 751BD-01 ISSUE O

| SYMBOL | MIN  | NOM      | MAX  |

|--------|------|----------|------|

| Α      | 1.35 |          | 1.75 |

| A1     | 0.10 |          | 0.25 |

| b      | 0.33 |          | 0.51 |

| С      | 0.19 |          | 0.25 |

| D      | 4.80 |          | 5.00 |

| E      | 5.80 |          | 6.20 |

| E1     | 3.80 |          | 4.00 |

| е      |      | 1.27 BSC |      |

| h      | 0.25 |          | 0.50 |

| L      | 0.40 |          | 1.27 |

| θ      | 0°   |          | 8°   |

**TOP VIEW**

**END VIEW**

# Notes:

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Complies with JEDEC MS-012.

#### **Table 7. ORDERING INFORMATION**

| Part Number  | Marking | Package Type                        | Temperature |

|--------------|---------|-------------------------------------|-------------|

| P2008AF-08ST | P2008AF | 8-PIN SOIC, TUBE, Pb Free           | Commercial  |

| P2008AF-08SR | P2008AF | 8-PIN SOIC, TAPE AND REEL, Pb Free  | Commercial  |

| P2008AF-08TT | P2008AF | 8-PIN TSSOP, TUBE, Pb Free          | Commercial  |

| P2008AF-08TR | P2008AF | 8-PIN TSSOP, TAPE AND REEL, Pb Free | Commercial  |

| P2008AG-08ST | P2008AG | 8 PIN SOIC, TUBE, Green             | Commercial  |

| P2008AG-08SR | P2008AG | 8-PIN SOIC, TAPE AND REEL, Green    | Commercial  |

| P2008AG-08TT | P2008AG | 8-PIN TSSOP, TUBE, Green            | Commercial  |

| P2008AG-08TR | P2008AG | 8-PIN TSSOP, TAPE AND REEL, Green   | Commercial  |

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registered readerlands of semiconductor Components industries, Ite (SCILLC) solicit esserves the right to make changes without further holice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

Europe, Middle East and Africa Technical Support:

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative